- 全部

- 默认排序

Cadence Allegro现在几乎已成为高速板设计中实际上的工业标准,最新版本是Allegro 17.4。与其前端产品Capture相结合,可完成高速、高密度、多层的复杂 PCB 设计布线工作。

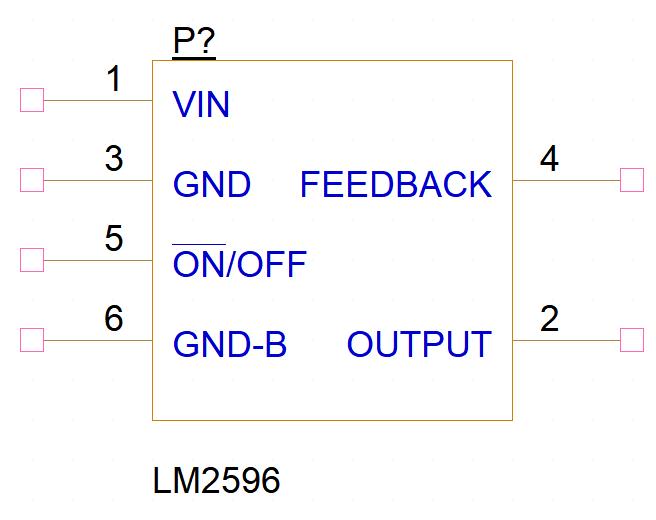

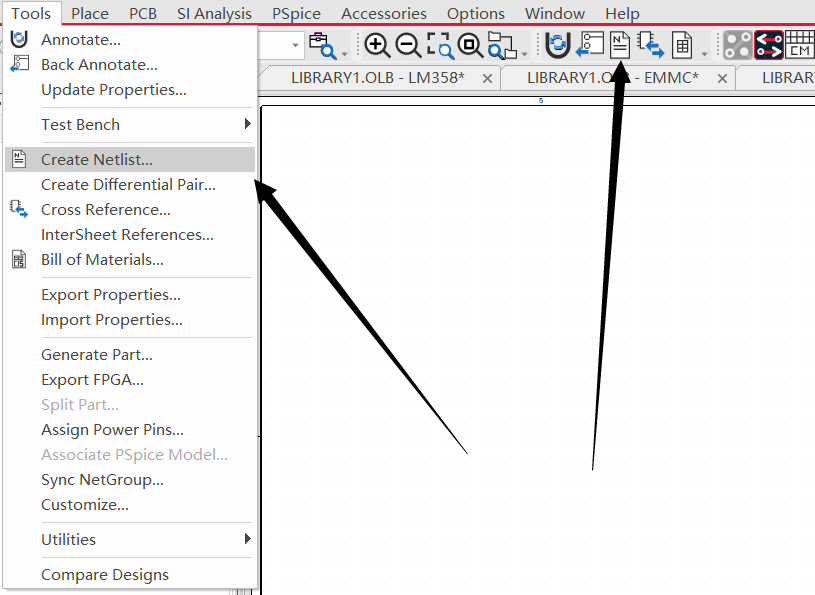

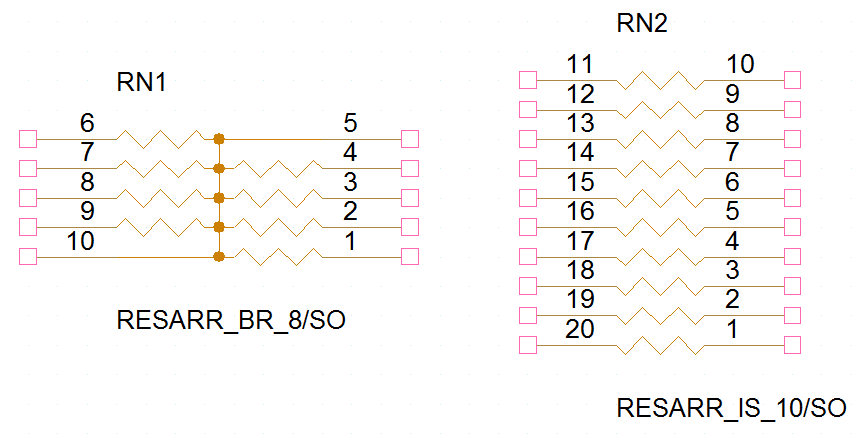

元件库开发环境及设计

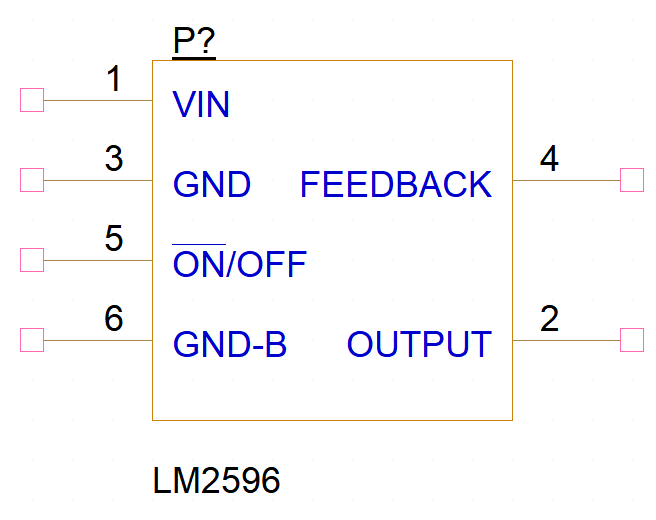

在用Allegro Capture绘制原理图时,需要放置各种各样的元件。虽然Cadence Allegro内置的元件库虽然很完备。但是难免会遇到找不到需要的元件的时候,因此在这种情况下便需要自己创建元件了。Cadence Allegro提供了一个完整的创建元件的编辑器,可以根据自己的需要进行编辑或创建元件。本章将详细介绍如何创建原理图元件库。

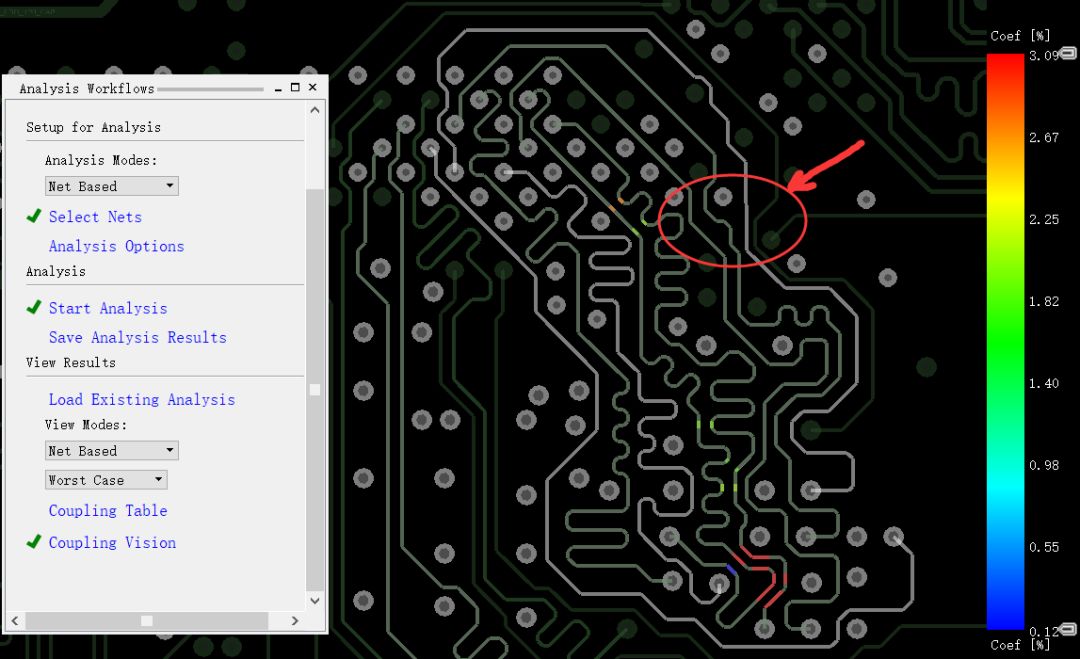

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

在项目实际的设计中我和小伙伴一样都遇到过很多麻烦的问题,有些时候原理图和PCB设计可能是由不同的工程师负责,由于种种原因可能需要在没有原理图的情况下直接对PCB进行操作。如更新元件封装和增加与删除元件等操作。接下来我们一起学习

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

2020年1月5日下午1点半,由21ic中国电子网举办的深圳线下网友技术分享沙龙在深圳市戴言有趣咖啡厅顺利进行。 参加本次活动的有21ic电子网论坛的高磊亮老师、林杰老师、马佳老师、黄勇老师等共7名资深版主、员工以及电子硬件爱好者。其中,黄勇老师代表凡亿教育作为特邀嘉宾参加了此次技术分享交流会。 黄勇老师作为凡亿教育的创始人,长期致力于Cadence Allegro高速PCB设计与Cadence Allegro高速PCB设计视频教学;具备丰富的PCB设计实战经验,尤其擅长高速信号数字类、消费

购买后联系助教拉入答疑群 随着电子技术的不断革新和芯片生产工艺的不断提高,印制电路板(PCB)的结构变得越来越复杂,从最早的单面板到常用的双面板再到复杂的多层板,电路板上的布线密度越来越高,同时随着DSP、ARM、FPGA、DDR

扫码关注

扫码关注